# Performance Evaluation of a Switched-Capacitor Voltage Pump Based Multilevel Inverter

Vijay Gound

M.Tech Student

School of Electrical & Electronics

Engineering

Scope Global Skills University,

Bhopal, M.P., India

Vijaygound1999@gmail.com

Sandeep Wasnik

Assistant Professor

School of Electrical & Electronics

Engineering

Scope Global Skills University

Bhopal, M.P., India

Balram Yadav

HOS

School of Electrical & Electronics

Engineering

Scope Global Skills University

Bhopal, M.P., India

**Abstract:** A multilevel inverter is a power electronic device that is used for high voltage and high power application because of its characteristics of generating a sinusoidal voltage based on several DC voltage levels. They give good quality output resulting with lower harmonic distortion in the output. This topology is designed based on switched-capacitor voltage pump technique and the number of output levels is defined by the number of switched-capacitor cells cascaded. Only one dc voltage source is needed and the problem of voltage balancing across the capacitor is avoided as well. A small input voltage can be used to generate a boosted output voltage, by switching the capacitors in parallel and in series. The basic MLIs are cascaded H-bridge (CHB), neutral point clamped, and flying capacitor inverters. In addition, the inverters inherit various advantages of the original structure, such as a high boost factor of 6, self-balanced capacitor voltages and reduced voltage ripples. Circuit description, operation principle, hybrid PWM modulation and capacitor voltage ripples are analyzed. The capacitor voltages are self-balanced as they are connected in parallel with the input voltage source for several instances in every fundamental cycle.

## I. INTRODUCTION

Multilevel inverter (MLI) is a breed of voltage source inverter (VSI), which can synthesize a high quality ac output voltage of required frequency from multiple separate/isolated dc sources (SDCs). The MLIs strikingly outperform the conventional three level

inverters (TLIs) with the apparent merits such as lower dv/dt and device stresses, a diminished output voltage distortion, a minimal switching losses and a reduced electro-magnetic interference (EMI). Since its supersession in 1975, many topologies have been illustrated, which are complex in structure with large number of components. In view of above facts, MLI has become an amenable solution to prevailing issues of the TLI, through which the integration of SDCs like batteries, super capacitors and solar panels has become doable. The MLIs, an improved the class in the VSI family, can establish a closer (staircase) shape to the sinusoidal wave and there by minimises the total harmonic distortion (THD). MLI structures actualize a higher system voltage, which is typically quite a few times more than the individual switch's blocking voltage. MLIs can synthesize an ac voltage of desired magnitude and frequency at a lower distortion level with a multiple control degrees of freedom. This unique characteristics is not available in the classical TLI. The evolution of MLI family started when its first pristine structure was introduced by R.H.Baker, which is a simple series connection/addition of H-bridges and called as cascaded H-bridge multilevel inverter (CHBMLI)

## II. NEED OF MLI

In the last few decades, industries have started to insist higher power capabilities, and the load demand has reached the megawatt level, very recently. Today, in the industrial milieu, modern ac drives of megawatt (MW)

range are required to connect to the medium voltage distribution network. The power electronic switches of such a high voltage are either not available or not economical. This emphasises the importance of MLI structures, where synthesis of medium voltages just by involving the low voltage devices are possible. The synthesize of the higher output voltage demands more number output levels, but not the voltage rating of an individual device. That is the power electronic switches with a lesser voltage specification can be utilized in a MLI structure designed for the higher voltage. The dv/dt rating required for the switches of MLI is much lesser than the switches employed in the TLI. MLIs could be successful in the renewable energy, electric vehicles and similar applications due to their minimal output distortion. Besides all the above advantages, the scope for the performance enhanced PWM strategies and component count reduction options in MLI are still open. Multilevel inversion is a voltage synthesising technique wherein near sinusoidal shape is engraved through staircase kind of wave through several input dc sources. This staircase waveform minimizes the THD. As the number of steps (stair) increases the THD deceases. To actualize such an ac waveform with multiple steps, a complicated circuit topology is required which may involves several dc sources, array of power switches, diodes to clamp the node voltages, etc. The higher number of steps increases the component count and also controls complexity. Every application decides an optimal number of levels by considering the compromise between complexity and distortion.

### III. POWER QUALITY PROBLEMS

Poor PQ issues eventually bring about monetary loss of the power system network. PQ chiefly concerns to keep up voltage and current profile i.e. any deviation in these parameters can make extreme harm the electrical utility and end shoppers. A diagram of numerous PQ issues alongside their causes and results are introduced.

**Voltage sag/dip:** - The voltage droop or plunge can be expressed as reduction in ostensible voltage level by 10-90% for brief term for half cycle to one moment as appeared in fig.1.1. At some point, voltage list keep going for long length such delayed low voltage profile alluded as 'under-voltage'. Voltage hang is additionally partitioned in three classifications: quick, fleeting and brief lists separately.

Figure 1.1: Voltage sag/dip

Voltage droop are predominantly caused because of event of faults in power system, overloading of the electrical network and beginning current drawn by substantial electrical loads like engines and refrigerators. Voltage sag in power system network results in failure of relays and contactor, dim light and fluctuating power.

**Voltage Swell:** - Voltage swell can be expressed as voltage rise by 10-80% of typical incentive for length of half cycle to one moment as appeared in fig.1.2.

Figure 1.1: Voltage Swell

Likewise voltage droop, delayed high voltage profile is eluded as 'finished voltage'. Voltage swell is subdivided as:

- Instantaneous swell

- Momentary swell

- Temporary swell

Voltage swell is for the most part caused by separation of substantial load, Single Line to Ground fault (SLG) brings about voltage ascension in undaunted phases and free association of impartial wire. Voltage swells brings about breakdown of protection, overheating of electrical hardware and harm to electronic gear.

**Voltage Interruption:** - Voltage intrusion can be expressed as diminishment in rms voltage by beneath 0.1 pu of ostensible or complete disappointment of supply voltage. It can be additionally partitioned into two classes in view of interruption time period:

### 1 Short interruption

If the intrusion span happens for few milli-seconds then it is named as short interference. This is because of breaking down of switching devices which may influence the information stored in sensitive devices like PLCs.

### 2 Long interruption

If the interruption duration occurs for range between few milli-seconds to several seconds then it is termed as long interruption as shown in fig.1.3.

Table 5.1 Output voltage and current with inductive load change

| Parameter           | Specification          |

|---------------------|------------------------|

| DC source (VDC)     | 100V                   |

| Output frequency    | 50Hz                   |

| switching frequency | 10kHz                  |

| Capacitor           | 4200uF                 |

| R load              | 50 $\Omega$            |

| RL-Load             | R=50 $\Omega$ ,L=100mH |

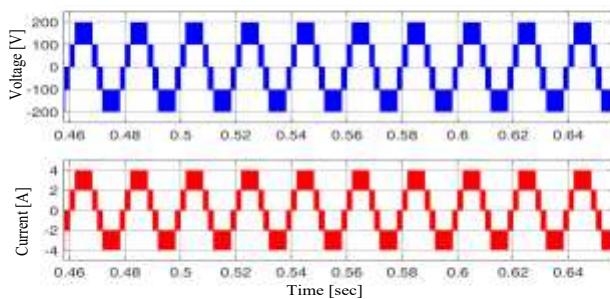

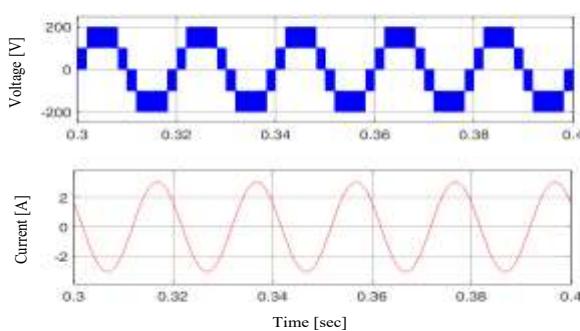

Figure 5.1 shows the load voltage and load current with resistive load of 50 Ohm. It archive five-voltage level at

Figure 1.2: Voltage signal with long interruption

## IV. OPERATION OF BOOST INVERTER

The operational states and capacitor parallel and series path (i.e., charging and discharging) for the proposed 5-Level inverter for a grid-connected PV power generation are shown in Table 4.1. It's worth noting that 1 and 0 represent the ON and OFF states of the power switches. " $\Delta$ " and " $\nabla$ " indicate the charging and discharging modes of the capacitor 'C'. The path through which capacitors are charged is shown in green, and the resistive load and inductive load current path are shown in blue and red.

Table 4.1: Switching table of proposed boost inverter

| Switching State | V <sub>ab</sub> | Power Switches |             |                |             |                |             | Capacitors (C) |

|-----------------|-----------------|----------------|-------------|----------------|-------------|----------------|-------------|----------------|

|                 |                 | S <sub>1</sub> | $\bar{S}_1$ | S <sub>2</sub> | $\bar{S}_2$ | S <sub>3</sub> | $\bar{S}_3$ |                |

| $\beta_1$       | 0               | 1              | 0           | 1              | 0           | 1              | 0           | $\Delta$       |

| $\beta_2$       | $+V_{DC}$       | 1              | 0           | 0              | 1           | 1              | 0           | $\Delta$       |

| $\beta_3$       | $+2V_{DC}$      | 0              | 1           | 0              | 1           | 1              | 0           | $\nabla$       |

| $\beta_4$       | 0               | 1              | 0           | 0              | 1           | 0              | 1           | $\Delta$       |

| $\beta_5$       | $-V_{DC}$       | 1              | 0           | 1              | 0           | 0              | 1           | $\Delta$       |

| $\beta_6$       | $-2V_{DC}$      | 0              | 1           | 1              | 0           | 0              | 1           | $\nabla$       |

## V. SIMULATION RESULTS

The results of proposed five-level structure are validated in MATLAB/Simulink environment. Table 5.1 displays the simulation parameters of the suggested work. The simulation result obtained under steady state and dynamic circumstances.

the output terminal and generates boost output voltage with levels of  $+200V$ ,  $+100V$ ,  $0$ ,  $-100V$  and  $-200V$ .

Figure 5.1 Output voltage and current with resistive load

Figure 5.2 Output voltage and current with inductive load

Figure 5.2 shows the load voltage and load current with inductive load of 50 Ohm and 100mH. It achieves five-voltage level at the output terminal and generates boost output voltage with levels of +200V, +100V, 0, -100V and -200V. Also, generates pure sinusoidal current at the output load terminal.

## VI. CONCLUSION

Compressors, conveyors, crushers, furnace blowers, grinding mills, pumps, rolling mills, mining hoists, and other modern industrial loads are operating with high voltages and power. Due to their drawbacks, which include the need for a greater number of power switches at higher  $di/dt$  and  $dv/dt$  ratings, conventional VSIs are no longer the preferred choice for high power applications. MLI's numerous advantages, including reduced THD, reduced EMI, and reduced switching device stresses, were recognized by a large number of power electronic researchers. As a result, MLI applications are expanding to include things like uninterrupted power supply (UPS), flexible AC

transmission system (FACTS), the conversion of solar and wind energy, fuel cell and electric vehicles.

Over the past four decades, numerous MLI topologies that are suitable for various high power and voltage applications have been developed by researchers.

**Conflict of Interest:** The corresponding author, on behalf of second author, confirms that there are no conflicts of interest to disclose.

**Copyright:** © 2025 by Vijay Gound, Sandeep Wasnik, Balram Yadav Author(s) retain the copyright of their original work while granting publication rights to the journal.

**License:** This work is licensed under a Creative Commons Attribution 4.0 International License, allowing others to distribute, remix, adapt, and build upon it, even for commercial purposes, with proper attribution. Author(s) are also permitted to post their work in institutional repositories, social media, or other platforms.

## REFERENCES

- [1] Y. Q. Wang Y. S. Yuan G. Li Y. M. Ye K. W. Wang and J. Liang "A T-type switched-capacitor multilevel inverter with low voltage stress and self-balancing" *IEEE Transactions on Circuits and Systems I: Regular Papers* vol. 68 no. 5 pp. 2257-2270 May 2022.

- [2] Ruijie Sun, Yuanmao Ye and Xiaolin Wang, "A Novel Five-Level Boosting Inverter With Self-Balancing Switched-Capacitor for Electric Vehicles", 8th International Conference on Power Electronics Systems and Applications (PESA), IEEE 2021.

- [3] Y. Q. Wang Y. S. Yuan G. Li T. J. Chen K. W. Wang and J. Liang "A generalized multilevel inverter based on T-type switched capacitor module with reduced devices" *Energies* vol. 13 no. 17 pp. 4406 Aug. 2021.

- [4] S. Habib M. M. Khan F. Abbas A. Ali M. T. Faiz F. Ehsan et al. "Contemporary trends in power electronics converters for charging solutions of electric vehicles" CSEE Journal of Power and Energy Systems vol. 6 no. 4 pp. 911-929 Dec. 2020.

- [5] P. Wang S. J. Ma S. Akram K. Zhou Y. D. Chen and M. T. Nazir "Design of archimedes spiral antenna to optimize for partial discharge detection of inverter fed motor insulation" IEEE Access vol. 8 pp. 193202-193213 Nov. 2020.

- [6] J. Zeng W. J. Lin D. H. Cen and J. F. Liu "Novel K-type multilevel inverter with reduced components and self-balance" IEEE Journal of Emerging and Selected Topics in Power Electronics vol. 8 no. 4 pp. 4343-4354 Dec. 2020.

- [7] W. J. Lin J. Zeng J. F. Liu Z. X. Yan and R. J. Hu "Generalized symmetrical step-up multilevel inverter using crisscross capacitor units" IEEE Transactions on Industrial Electronics vol. 67 no. 9 pp. 7439-7450 Sep. 2020.

- [8] K. P. Panda P. R. Bana and G. Panda "A switched-capacitor self-balanced high-gain multilevel inverter employing a single DC source" IEEE Transactions on Circuits and Systems II: Express Briefs vol. 67 no. 12 pp. 3192-3196 Dec. 2020.

- [9] M. Ghodsi and S. M. Barakati "New generalized topologies of asym-metric modular multilevel inverter based on six-switch H-bridge" International Journal of Circuit Theory and Applications vol. 48 no. 5 pp. 789-808 May 2020.

- [10] M. Ghodsi and S. M. Barakati "A generalized cascade switched-capacitor multilevel converter structure and its optimization analysis" IEEE Journal of Emerging and Selected Topics in Power Electronics vol. 8 no. 4 pp. 4306-4317 Dec. 2020.

- [11] AbderezakLashab, Dezso Sera , Frederik Hahn , Luis Camurca, YacineTerriche, Marco Liserre, and Josep M. Guerrero, "Cascaded Multilevel PV Inverter With Improved Harmonic Performance During Power Imbalance Between Power Cells", IEEE Transactions on Industry Applications, Vol. 56, No. 3, May/June 2020.

- [12] W. Peng Q. Ni X. Qiu and Y. Ye "Seven-Level Inverter With Self-Balanced Switched-Capacitor and Its Cascaded Extension" IEEE Trans. Power Electron. vol. 34 no. 12 pp. 11889-11896 Dec. 2019.

- [13] M. Saeedian M. E. Adabi S. M. Hosseini J. Adabi and E. Pouresmaeil "A Novel Step-Up Single Source Multilevel Inverter: Topology Operating Principle and Modulation" IEEE Trans. Power Electron. vol. 34 no. 4 pp. 3269-3282 April 2019.

- [14] J. Liu W. Lin J. Wu and J. Zeng "A Novel Nine-Level Quadruple Boost Inverter with Inductive-load Ability" IEEE Trans. Power Electron. vol. 34 no. 5 pp. 4014-4018 May 2019.

- [15] W. Peng Q. Ni X. H. Qiu and Y. M. Ye "Seven-level inverter with self-balanced switched-capacitor and its cascaded extension" IEEE Transactions on Power Electronics vol. 34 no. 12 pp. 11889-11896 Dec. 2019.

- [16] R. Barzegarkhoo M. Moradzadeh and F. Blaabjerg "A new boost switched-capacitor multilevel converter with reduced circuit devices" IEEE Trans. Power Electron. vol. 33 no. 8 pp. 6738-6754 Aug. 2018.