# A Review on PWM Based Multicarrier Multilevel Inverter with Reduced Number of Switches

Sandeep Kumar

M. Tech. Scholar

Department of Electrical and Electronics Engineering, Vedica

Institute of Technology

Bhopal, India

sandeep.kumar41991@gmail.com

Abhimanyu Kumar

Assistant Professor

Department of Electrical and Electronics

Engineering, Vedica Institute of Technology

Bhopal, India

ies.abhi@gmail.com

**Abstract:** With increasing demand for high power energy which is fulfilled by use of semiconductors with higher voltage and current to execute such applications. In order to derive high power from medium power-based semiconductors, multilevel inverters are considered to be best solution with advantages over conventional resources. An advanced multi-level inverter topology is offered to optimize the number of switches and improve THD.

**Keywords:** PWM, Multilevel Inverter, Total harmonic distortion.

## I. INTRODUCTION

The converters must be designed to provide high quality output voltage or current waveform with minimal ripple. However, in high power and high voltage applications, conventional two-stage inverters have some limitations in high frequency operation, mainly due to the switching losses and power supply limits of the power supplies. Many industrial applications have started to demand high-performance devices in recent years. For electricity control or energy conditioning, it is necessary to convert electricity from one form to another and the switching characteristics of power devices allow these conversions. Inverters are the gadgets used to change over direct current into alternating current. The yield voltage of an inverter can be fixed or variable with a fixed or variable recurrence. A variable yield voltage can be acquired by changing the DC input voltage and keeping the inverter consistent. Then again, if the DC voltage is fixed, it is conceivable to get a variable yield voltage by fluctuating

the addition of the inverter. Inverter gain is characterized as the connection between the AC yield voltage and the DC input voltage. In customary two-phase inverters, the information DC voltage is changed over into an AC power gracefully with the ideal recurrence and voltage through strong state circuit breakers. Contingent upon the setup, four or six switches are utilized. One gathering of switches gives the positive half-wave at the yield, called the positive gathering switch, and the other gathering, which gives the negative half-wave, is known as the negative gathering.

### Limitations of Conventional Inverters

1. The traditional two-level UPS generates an output with a level of 0 or + VDC or – VDC

2. Due to the higher frequency, they cannot be used for high power and high voltage applications because they cause switching losses.

3. The waveform of the ideal inverter output voltage must be sinusoidal, but that of conventional inverters is not sinusoidal and contains some harmonics.

4. A large capacitor is connected to the DC power source, which is expensive and requires more space.

In order to overcome these drawbacks multilevel inverters are introduced.

## II. MULTILEVEL INVERTERS

Multilevel inverters have received a lot of attention in high-performance electronic applications because they meet the needs of higher performance and reduction of output harmonic distortion, voltage ( $du / dt$ ) and EMI

phenomena. The 3-level converter started the multi-stage process and several multi-level converter topologies have been developed. Multistage inverters offer more than 2 voltage levels. The basic principle of a multistage inverter is to connect the static switches in series so that they can operate at nominal powers of different megavolts and at medium voltage levels (from 1 kV to 35 kV) higher than the rated values of the various automatic circuit breakers. The output voltage waveform is synthesized from various levels of capacitor voltage sources. As the number of levels increases, the resulting output waveform approaches the sine with less distortion, less switching frequency and greater efficiency.

#### A. Basic Principle of Operation

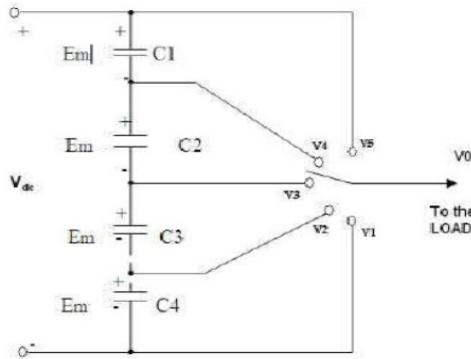

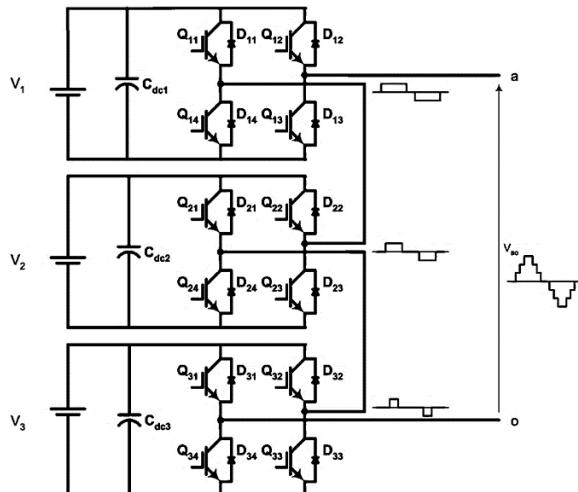

Multilevel inverter diagram is shown in figure 1.1 in which output voltage is represented as  $V_o$ . This voltage is termed as arbitrary voltage level based on selection of voltage levels of  $V_1, V_2, \dots$ . Therefore, this is termed as multilevel switching inverters. In such architecture a series of capacitors are connected and acts as reserve of energy for inverters and also supplies energy to other switches of such architectures that are connected in multiple levels to generate multiple output level and such desired output levels are reached.

**Fig 1: Schematic of Single Pole of Multilevel Inverter by a Switch**

For associate  $m$ -level electrical converter desires  $(m-1)$  capacitors. the foremost attractive features of multilevel inverters area unit as follows.

- It is feasible to provide output voltages with very low distortion and reduced distortion.

- Consume input current with very small distortion.

- They may be used with a lower shift frequency.

- A multistage UPS will eliminate the requirement for a transformer and cut back the harmonics generated by the electrical converter.

- With extra voltage levels, the voltage curve has a lot of free switch angles, which may be preselected to eliminate harmonics. The main disadvantage of multilevel inverters is that they need a larger number of switches.

### III. TYPES OF MULTILEVEL INVERTERS

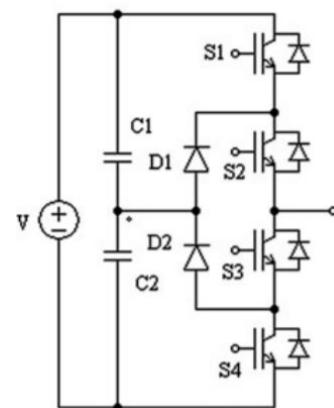

#### A. Diode Clamped Multilevel Inverter

Generally in the multi-level inverter diodes are used as a clamping device in order to fix the DC voltage and optimal voltage output levels are generated. In this type of multilevel inverter, diodes are used to limit the voltage load on power devices. The  $V_{DC}$  voltage is applied to each capacitor end and switches. In order to generate  $n$  level of voltage output,  $(n-1)$   $V_{DC}$  are required along with  $(n-2)$  diodes and  $(n-1)$  switching devices. As the number of voltage levels are increased, the quality of generated waveform increases and generate more refined sine waveform.

**Fig 2: Multilevel Inverter with Diode Clamped**

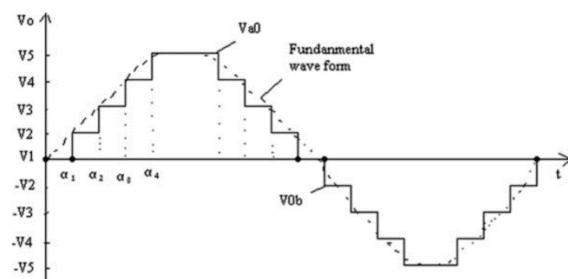

**Fig 3: Output Voltage Waveforms with 5 Levels**

#### B. Flying Capacitors Multilevel Inverter

Compared to diode and H-bridge inverters, the multi-level H-bridge flight condenser inverter (HBFCMLI) is the new topology. By selecting the switching state, the flying

capacitor has some significant advantages over the lack of diodes in the blocked diode and regulates the voltage of the flying capacitor. In many industrial applications, flying capacitors are used because of these advantages.

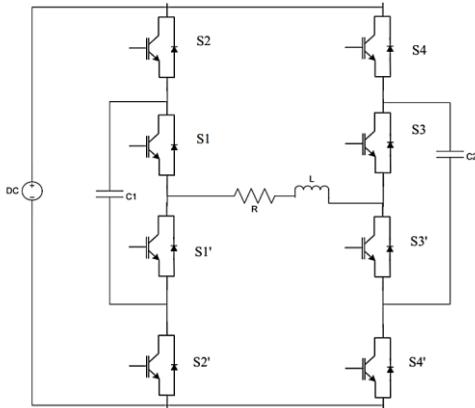

**Fig 4: Flying Capacitors Multilevel Inverter**

The HBFCMLI converter, a capacitor, plays no role in voltage equalization. There are probably changes in the voltage ratio and they decrease to increase the voltage level improving the quality of the current. The study of multistage converters with flying capacitors with three different voltage levels, based on THD, the three different voltage levels, compensates the converter with flying capacitors. With these three different voltage levels, it is an important property that guarantees operational safety and efficiency. The topology of the 5-stage H-bridge flight condenser (HBFC) is shown in Fig. 1.4. The configuration of the multistage inverter with H-bridge flight capacitor has a positive group and a negative group, since each cell has two complementary switches. To provide the positive waveform through the load, the positive cell group is routed and therefore the number of voltage levels increases with increasing number of cells. Thanks to the phase-shifting pulse width modulation technology, it is used to control complementary switches. Using the formalism of specular speculation, the H-bridge converter got its one-legged prototype. The circuit has 16 switching states. Capacitors  $C_1$  and  $C_2$  are flying capacitors and their voltages  $V_{c1}$  and  $V_{c2}$ , respectively. The capacitor voltages are equal to  $V_{c1} = V_{c2}$ . The voltages of the capacitor which are controlled so as to be adjusted accordingly to  $-V_{DC}/4$ ,  $V_{DC}/2$  and  $V_{DC}/4$ .

### C. Cascaded Multilevel Inverter

Cascade multilevel inverters, as one of the main categories of multilevel inverters, have received more attention in high power and high voltage applications. The

multi-level inverter generates a desired AC output level by using multiple DC voltage sources as inputs. By expanding the quantity of DC voltage sources on the information side, a sinusoidal yield waveform is created. This capacity expands the force nature of the yield waveform and diminishes lower request sounds. The course staggered inverter comprises of a few base units associated in arrangement. The geography of each base unit is the equivalent and each base unit is worked as a bundle. By evacuating a base unit, the inverter at that point works regularly with a decreased number of created yield levels. Unwavering quality and particularity are in this way two different points of interest of this inverter. What's more, an essential recurrence control strategy can be utilized in this inverter, which brings about low exchanging misfortunes. The straightforward activity and the chance of utilizing circuit breakers with low evaluated voltages are further favorable circumstances of this inverter. These highlights decrease the multifaceted nature and in general expense of the UPS. Then again, countless required segregated DC voltage sources, expanding the quantity of yield levels produced, is the primary hindrance of course inverters.

A type of cascaded multilevel inverter is termed as H-Bridge inverter. This inverter is called a symmetrical cascade inverter, which implies a high degree of modularity. In this inverter, taking into account the  $n$  numbers of H-bridge with  $(2n + 1)$  levels which are generated at the output. For example, taking into account  $n = 2$ , voltage levels of  $\pm 2 V_{DC}$ ,  $0$  and  $\pm 1 V_{DC}$  are generated at the output. The main problem with this inverter is the high required number of isolated gate bipolar transistors (IGBTs) and DC voltage sources increasing the number of output levels generated due to the same size as its DC voltage sources. Therefore, various algorithms were presented to determine the size of the DC voltage sources for the cascade multistage H-bridge inverter.

**Fig 5: Functional Block Diagram**

The principle favorable position of these inverters is to expand the quantity of yield levels created. The primary inconvenience of these inverters is the utilization of circuit breakers with high appraised voltage esteems, which prompts an expansion in the expense of the inverter. As a result, numerous other symmetric and asymmetric cascade inverters have been implemented. These inverters can increase the number of output levels by reducing the number of circuit breakers or IGBTs or DC voltage sources.

Distinctive balance methodologies are workable for multi-stage inverters. The quantity of triangular waves is contrasted and a controlled sinusoidal tweak signal. The quantity of transporters required to create level  $m$  yield is  $m-1$ . Various degrees of opportunity are accessible in the vector-based multistage PWM. The standard of the transporter based PWM technique is to utilize transporter  $m-1$  with a reference signal for an inverter of level  $m$ . There are degrees of opportunity in recurrence, plentifullness, stage, DC balance and various substance of the third consonant of the carrier and the reference signal.

#### IV. PWM STRATEGIES

Multilevel inverters have received a lot of attention due to their low electromagnetic interference and reduced harmonic distortion. The most common PWMs discussed in the literature are flywheel diode clamp capacitors and H bridge PWMs in cascade. Blocked diode PWMs have irregular transition DC voltage levels. This distorts the output waveform, creating more harmonics in the system. The number of diodes used for such an inverter at a higher level is significantly very high compared to other techniques [1, 2]. The flying capacitor MLI is similar to

its predecessor, with its diode replaced by a capacitor. This topology also has a similar drawback, which requires additional capacitors at higher levels, which increases the complexity of the circuit [3, 4]. Cascading H-bridge topology has recently gained popularity because a number of components require a minimum number of components [5-8]. Numerous control strategies are used to improve converter performance [9-11]. Higher PWM values require multiple switches that operate at high frequency. This results in high switching losses in the topology. The main concern of MLI design is the creation of a topology that uses a small number of switches at each operational level [12]. Line and switching losses are high in a PWM presented in series. The switches involved in operation at the highest levels for the circuit are very large.

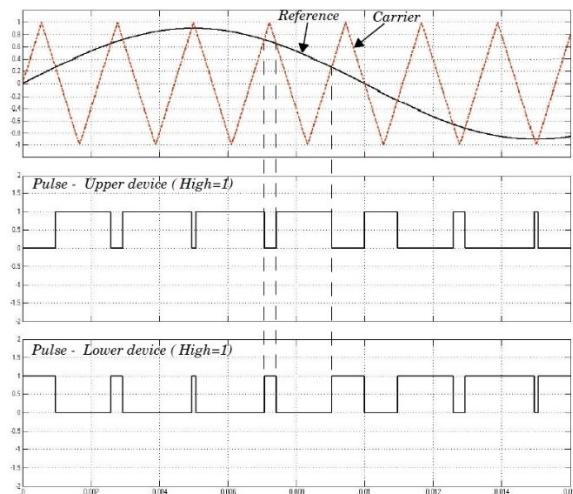

In a pulse width modulated inverter, each half wave of the output voltage is made up of several square pulses of appropriate width instead of a single square wave. The principle of PWM voltage inverters can be represented in the same way as current converters. In both cases, the goal is to produce an approximately sinusoidal output voltage by varying its "average" sinusoidally.

The sinusoidal pulse width modulation technique involves pulses with different work cycles but constant amplitude for each period. To generate the SPWM signal, the carrier wave of the triangle is conventionally compared with the sine wave of the operating frequency. The repetition of the Simulink sequence block is used to generate the triangular waveform. The comparison operator is used as a comparator to generate pulse signals. The carrier wave frequency is chosen as 10 kHz and the sine wave frequency is 50 Hz (base frequency).

Switching is prepared several times per half cycle, then the pulse width is shifted to change the output voltage. SPWM generates the efficiency of the inverter with reduced lower order interference. It is conceivable that the sampling frequency presents a high contrast with the central elongation frequency of the inverter.

The peak of the sinusoidal modulation waveform is less than the peak of the waveform of the triangular carrier voltage. If the sine waveform is larger than the triangular waveform, the upper switch is turned on and the lower switch is turned off.

In addition, the upper switch is turned off and the lower switch is active when the sine waveform is smaller than the triangular waveform. Depending on the switching states, a positive or negative intermediate circuit voltage

is applied to each phase. The pulse width depends on the intersection of the triangular and sinusoidal waveforms.

**Fig 6: Generation of PWM**

#### V. MULTICARRIER PULSE WIDTH MODULATION

The waveforms of the practical inverters are not sinusoidal and contain more power than some lower order harmonics. Rectangular and nearly square waveforms may be acceptable for low and medium power applications, but sine waveforms with less distortion are required for high power applications. The harmonic content present at the inverter output between direct and alternating current can be removed using a filter circuit or by using pulse width modulation circuits. The disadvantage of using filters is that they have larger units, higher losses and therefore lower efficiency, which leads to higher implementation costs, while the use of PWM techniques reduces requirements. Minimum or no filter depending on the type of application and control. Generation of ignition pulses for circuit breakers and type of application.

#### VI. LITERATURE REVIEW

Ray et al. [1] used Space Vector Pulse Wide Modulation (SVPWM) technique for generating 17 level output voltage level and achieved 7.86% THD.

KarthiKeyan. V et al. [2] in this document simulation analysis and a case study area unit performed to work out the influence of irradiance on the efficiency issue of the electrical phenomenon system connected to the network. Nowadays, alternative energy is that the energy resolution for several applications. It may an isolated scheme that has the inaccessible space or a system connected to the

network. The isolated electrical phenomenon scheme is permanently connected to a device to store excess energy once the present generated is quite comfortable. Network-connected solar systems area unit a lot of reliable. Since the electrical phenomenon scheme is fed directly into the grid, interconnection poses several issues because of the intermittent nature of the input power. The most reasons for power fluctuations area unit changes in irradiation and temperature.

Prabaharan Natarajan et al. [3] a new design of the multilevel UPS configuration is proposed to cut back the quantity of parts and improve the standard of the wave form during a electrical phenomenon system. The projected configuration operates within the binary uneven condition to get the output voltage level with wide amplitude and low harmonic distortion. A triangular single-pole trapezoidal reference is employed to get the specified change pulses to provide the specified output voltage level. The projected configuration needs eight single-pole switches to provide the 31-level output voltage level and 3.18% total harmonic distortion while not the employment of filters. the price of Total Harmonic Distortion (THD) conforms to the IEEE 519 harmonic customary. The DC supplys separated by the proposed configuration area unit replaced by the arrangement of the photovoltaic modules to check the configuration with the renewable energy source.

Munilakshmi et al. [4] solar power is one in every of the renewable energies wont to generate energy from electrical phenomenon systems. The DC-DC convertor is employed to extend the DC voltage of electrical systems. And the system of the solar energy is thus connected to an electrical converter for AC applications conventional inverters because several issues, such as non-sinusoidal output, high harmonic distortion (THD), high switch stress and a greater number of switches. The Consequently, multi-level inverters (MLI) became very important compared to conventional inverters for top voltage and high power applications because of the rise within the variety of voltage levels that turn out fewer harmonics. This document proposes a multi-level cascade electrical converter with a minimum number of switches that may be used in alternative energy cooling applications. The projected topology are the consist of the twenty five output levels using ten near-sinusoidal output switches that reduces the gate control circuit and optimizes the circuit configuration. Multi-level uneven

inverters are a lot of advantageous than symmetrical multi-level inverters to get a greater number of output levels using an equivalent number of the voltage source inverter. The other benefits of the projected topology are reduced stress and a discount in THD.

Karthikeyan V et al. [5] this study of the new multi-level electrical converter with a reduced variety of switches and non-identical DC sources is conferred. Compared to ancient inverters, this electrical converter generates additional output levels with fewer switches, reducing harmonics and improving power quality. The switch angles of every output level are determined using an easy sinusoidal characteristic to scale back the output harmonics. The simulation of a 33-stage multi-level asymmetrical UPS with a reduced range of switches is performed with MATLAB / Simulink and therefore the results are conferred. The reduced content of voltage harmonics and output current is reduced to IEEE standards.

Palanisamy Kaliannan et al. [6] this article presents a brand new single-phase multi-level hybrid electrical converter with a minimum variety of switches for an electrical phenomenon application. A follow of the utmost power points Perturb and Observ permits you to follow the maximum power of the star module. A lift convertor is used to extend the voltage generated as a result of the projected electrical converter operates in an asymmetrical state. The projected electrical converter is that the combination of a reduced switch topology and an H bridge cascade topology. 2 types of sinusoidal reference part displacement carrier arrays are won't to generate gate pulses for the carrier. Projected electrical converter. It produces an output voltage of fifteen levels with 8.12% of the overall harmonic distortion.

VenuSonti et al. [7] This document presents a PWM (Pulse width Modulation) technique to reduce the leak current in inverters independent of the grid / while not PV. The projected PWM technique is integrated with the MPPT formula and is applied to the CMLI at 5 levels. Moreover, using the projected PWM technique, high frequency voltage transients in common mode and common mode voltages area unit reduced to a minimum. Therefore, the proposed PWM technique minimizes the electrical phenomenon generator leak current and therefore the EMI filter necessities within the system while not the necessity for extra switches. Moreover, this

text presents the voltage analysis at the terminals of the electrical phenomenon generator and therefore the common mode voltage of the electrical converter using the switch operate. Mistreatment the analysis provided, the impact of the PWM technique may be analyzed as a result of it directly links the switch operate to the common mode voltage and to the leak current. The proposed PWM technique additionally requires a reduced carrier count compared to the conventional curving pulse dimension modulation technique for the given CMLI. This text presents all the small print of the operational principle and analysis, with support for simulations and experimental results of the proposed PWM technique.

Raghavendra Reddy Karasani et al. [8] this document presents a topology of the three-phase modular multi-level cascade electrical converter derived from the projected changed H-bridge module. This topology reduces the number of circuit breakers, losses, installation space, voltage load and converter costs. For environments that use renewable energies, like photovoltaic (PV) systems connected to the micro-array system, the electrical device allows reduced operation and higher power quality. This multistage UPS is a good strategy for the electronic power interfaces of renewable energy systems. The basic operations of a single module and therefore the hybrid topology proposed in a cascade are explained. The power to work in each symmetrical and asymmetrical modes is analyzed. Benchmarking is performed with conventional H-bridge cascade inverters and cascade Flying-Capacitor cascades. The following level control methodology is used to get the management signals for power semiconductor switches. To validate the applicability and performance of the projected structure in a photovoltaic environment with renewable energies, the results of the MATLAB / Simulink simulation are performed in stable and dynamic conditions. The experimental results are given to validate the simulation results.

HiralalSuryawanshi et al. [9] proposed diode clamed multilevel inverter for single-phase. The most inverters may be created by cascading MSDU. A comparative analysis is performed with different topologies. The projected topology involves a discount within the number of circuit breakers, losses, installation space, voltage load and convertor costs. The NLC technique (Nearest Level Control) is used to generate gate breaker signals. To verify the performance of the projected structure, the simulation

results are performed by a PSIM in both stationary and dynamic conditions. The experimental results are given to validate the simulation results.

C.R. Balamurugan et al. [10] in this study, totally different switch methods area unit developed for multi-level inverters (MLI). The switch methods projected in this article allow you to match totally different methods and to predict the exact switch methodology for different applications counting on the standard of the output. The electrical converter power is analyzed mistreatment Doctor of Theology (Total Harmonic Injection), VRMS (fundamental), CF (peak factor), FF (form factor) and DF (distortion factor) technologies. From the various non-PWM (Pulse width Modulation) and PWM methods, the analysis is used to work out the exact PWM strategies for particular applications.

G. Vijaykrishna et al. [11] this article presents the voltage reversal strategy for a multistage UPS to enhance induction motor performance by reducing harmonic distortion with an optimum number of switches. Method: the SPWM-PD technique was implemented to get network control signals to control 7-level multilevel inverters and nine reverse voltage levels, which needs only 3 carrier signals instead of six classic multi-level inverters. Results: the increase in levels throughout this strategy leads to a fast reduction of the harmonics of the output voltage and improves the standard of the ability supply to the UPS output with a voltage strategy of seven and nine inversions. you want a small total number of switches that can reduce switch losses during this process. The seven and 9-stage three-phase electrical converter is designed for R-L and R-L and three-phase induction motors. Improvements: the MATLAB / Simulink software implemented a seven and nine step inverted voltage UPS. The simulation results show that 9-stage inverters work higher than 7-D inverters with a lower thd and better current quality.

Kaustubh P. Draxe et al. [12] This document proposes an asymmetric multi-level cascade electrical converter with a minimum number of switches that may be employed in solar energy cooling applications. The proposed topology consists of twenty five output levels using ten near-sinusoidal output switches that reduces the gate control circuit and optimizes the circuit configuration. Multi-level asymmetric inverters are more advantageous than symmetrical multi-level inverters to obtain a greater

number of output levels using the same number of voltage sources. The other benefits of the projected topology are reduced stress and a reduction in thd. The thd for the projected electrical converter circuit is only 4.98%. Modeling and simulation area unit performed with MATLAB / SIMULINK. Solar energy is one of the renewable energy sources used to produce electricity using photovoltaic systems. The DC-DC device is employed to extend the DC voltage of electrical phenomenon systems associate degreed is therefore connected to an electrical converter for AC applications. Conventional inverters pose many issues, like non-sinusoidal output, high harmonic distortion (THD), high switch stress and a greater number of switches. Consequently, multi-level inverters (MLI) became important compared to conventional inverters for high voltage and high power applications due to the increase within the number of voltage levels that produce fewer harmonics.

Kaustubh P. Draxe et al. [13] solar power is one in all the renewable energy sources used to produce electricity using photovoltaic systems. The DC-DC converter is used to increase the DC voltage of electrical phenomenon systems and is thus connected to an electrical converter for AC applications. Typical inverters pose several issues, like non-sinusoidal output, high harmonic distortion (THD), high switch stress and a greater number of switches. Consequently, multi-level inverters (MLI) became very important compared to conventional inverters for high voltage and high power applications due to the increase within the number of voltage levels that produce fewer harmonics. This document proposes an uneven multi-level cascade electrical converter with a minimum number of switches that may be used in solar power cooling applications. The projected topology consists of twenty five output levels using ten near-sinusoidal output switches that reduces the gate control circuit and optimizes the circuit configuration. Multi-level asymmetric inverters are a lot of advantageous than symmetrical multi-level inverters to obtain a greater number of output levels using the same number of voltage sources.

Rakesh Kumar et al. [14] this article proposes a multistage UPS with fewer switches. Compared to conventional inverters, the proposed 17-level VR topology provides a higher PWM level, reducing harmonics. The use of an H bridge plays a key role in reducing the number of

switches, especially for higher levels. Here, a new sine-owned methodology is implemented to adjust the step angles for each output level to reduce the harmonics within the output wave form. The simulation is performed using the MATLAB software system package and also the results are displayed for the R and RL loads. An equivalent is extended to 3 phases. The reduced harmonic content is reduced to IEEE standards.

Jamuna V et al. [15] this article proposes a multi-level electrical converter with a reduced number of switches. Compared to conventional inverters, the proposed 17-level VR topology provides a higher PWM level, reducing harmonics. The use of an H bridge plays a key role in reducing the number of switches, especially for higher levels. Here, a new sine-owned methodology is enforced to adjust the step angles for every output level to reduce the harmonics within the output wave form. The simulation is performed using the MATLAB software package and the results area unit displayed for the R and RL loads. the same is extended to 3 phases. The reduced harmonic content is reduced to IEEE standards.

## VII. CONCLUSION

An electric inverter is basically a circuit that converts a direct current signal into an alternating current signal. The AC signal is most useful in our everyday devices and can be easily transmitted. Environmentally friendly energies such as wind and solar energy can be used and converted to alternating current. To convert the DC signal to an AC signal, we need to quickly change the DC signal and get more levels. It becomes a stair wave close enough to a sine wave. So, it is needed to control the switching topology that can reduce THD and at the same time improve voltage. Different positions of switches, determine different voltage levels.

## REFERENCES

- [1] R. Ray, M. A. Shadh and M. S. Reza, "Cascaded H-Bridge Multilevel Inverter Using SVPWM Modulation," International Conference on Advances in Science, Engineering and Robotics Technology (ICASERT), Dhaka, Bangladesh, 2019, pp. 1-5.

- [2] KarthiKeyan. V, Janarthanan S "Yield Factor of Grid Connected Solar Photovoltaic System-A Case Study" January 2017.

- [3] Prabaharan Natarajan, SaravananSubramani "A Reduced Switch Asymmetric Multilevel Inverter Topology Using Unipolar Pulse Width Modulation Strategies for Photovoltaic Application" DOI: 10.5772/67863 June 2017.

- [4] B.Munilakshmi, Dr.M.BalaSubba Reddy "A New Control Topology of A Cascaded Multilevel Inverter For Solar Applications" Special Issue-5ISSN: 2349-6495(P) | 2456-1908(O) 2017.

- [5] Karthikeyan V and Jamuna "Multilevel Inverter with Reduced Number of Switches for Solar Energy Generation" Volume VI, Issue VI, June 2017 | ISSN 2278-2540.

- [6] PalanisamyKaliannan, Prabaharan Natarajan "A Single Phase Grid Connected Hybrid Multilevel Inverter for Interfacing Photovoltaic System" DOI: 10.1016/j.egypro.2016.11.281 December 2016.

- [7] VenuSonti, Sachin Jain "Analysis of Modulation Strategy for the Minimization of Leakage Current in the PV Grid Connected Cascaded Multi-Level Inverter" DOI: 10.1109/TPEL.2016.2550206 January 2016.

- [8] Raghavendra Reddy Karasani, V.B. Borghate "A Three Phase Hybrid Cascaded Modular Multilevel Inverter for Renewable Energy Environment" DOI: 10.1109/TPEL.2016.2542519 March 2016.

- [9] HiralalSuryawanshi, PrafullachandraMeshram "A Modified Switched-diode Topology for Cascaded Multilevel Inverters" DOI: 10.6113/JPE.2016.16.5.1706 September 2016.

- [10] C.R. Balamurugan, S.P.Natarajan "A Review on Modulation Strategies of Multi LevelInverter" DOI: 10.11591/ijeecs.v3.i2.pp681-705 September 2016.

- [11] G. Vijaykrishna, O. Chandra Shekhar "A three phase 7-level and 9-level reversing voltage multilevel inverter" DOI: 10.17485/ijst/2015/v8i23/70612 January 2015.

- [12] Kaustubh P. Draxe , Mahajan SagarBhaskarRanjana "A cascaded asymmetric multilevel inverter with minimum number of switches for solar applications" Power And Energy Systems: Towards Sustainable Energy, 2014.

- [13] Kaustubh P. Draxe, Mahajan SagarBhaskarRanjana "A Cascaded Asymmetric Multilevel Inverter withMinimum Number of Switches for Solar Applications" 2014 Power and Energy Systems: Towards Sustainable Energy (PESTSE 2014).

- [14] Rakesh Kumar, KarthiKeyan. V "A MULTILEVEL INVERTER WITH REDUCED NUMBER OF SWITCHES" Conference: National Conference on Power Systems Power Electronics and Drives - 2013 March 2013.

- [15] Jamuna V, KarthiKeyan. V "A Multilevel Inverter With Reduced Number Of Switches" March 2013.